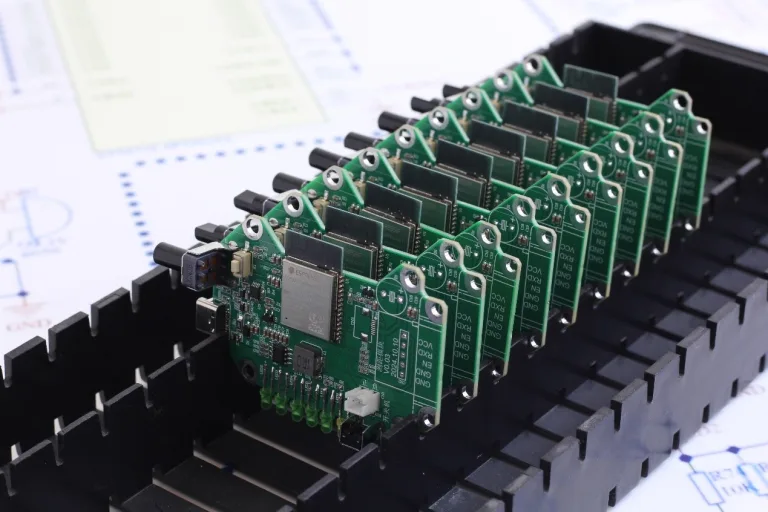

In real-world hardware development, EMC performance is one of the most challenging aspects of PCB engineering. For PCB 4-layer board design, questions such as how to arrange the stack-up, how power/ground planes affect EMC, and how vias and high-speed signals interact all play a decisive role in product stability and certification success.

To help engineers better navigate these challenges, this article provides a structured guide to EMC-aware PCB 4-layer design, covering stack-up strategies, via parasitics, routing rules, and practical considerations for real applications.

1. Preferred Stack-Up Options for PCB 4-Layer Board Design

Common pcb stack-up design solutions include:

Option 1 (Recommended)

Most widely used:

TOP / GND1 / PWR1 / BOTTOM

Option 2

Used when key components are placed on BOTTOM or important signals require bottom-layer routing.

Option 3

For through-hole–dominant boards; PWR on S2, BOTTOM as ground to form a shielding cavity.

2. Key Considerations in PCB 4-Layer Board Stack-Up Design

Signal layer = positive output

Power layer = negative output (copper removal)

Stack-up steps include schematic design, PCB import, preliminary placement, and defining:

- Layer count

- Units

- Pullback for 20H rule

- Naming planes (GND, PWR)

3. Via Design in PCB 4-Layer Boards

Types of Vias

- Through-hole Via

- Blind Via

- Buried Via

By Function

- Signal via

- Power/Ground via

- Thermal via

4. Via Structure and Parasitic Effects

Components

- Drill

- Pad

Common sizes: 0.2mm (drill), 0.4mm (pad).

Parasitic Capacitance

Slows signal rise time; formula:

C = 1.41εTD1/(D2 − D1)

Parasitic Inductance

More harmful in high-speed circuits; reduces decoupling effectiveness.

Formula:

L = 5.08h[ln(4h/d)+1]

5. Via Usage Guidelines

- Use larger vias for power/ground

- Smaller vias for high-speed signals

- Differential pairs must use symmetric via placement

- Multiple vias reduce equivalent inductance

- Microvias recommended for dense 4-layer designs

6. Routing Steps in PCB 4-Layer Board Design

- Start with the most complex area

- Route by functional modules

- Handle remaining low-priority nets

7. Routing Rules for PCB 4-Layer Boards

- Key/high-speed signals get highest priority

- High-density areas first

- Maintain small return loops

- Avoid sensitive signal routing between PWR and GND planes

- Follow impedance-control requirements

Successful PCB 4-layer board design requires not only theoretical knowledge but also extensive engineering experience. Stack-up choices, PCB EMC design, power integrity (PI), parasitic control, and routing strategies all influence product stability, certification success, and mass-production yield.

Tronixv provides end-to-end hardware development services for medical devices, industrial systems, AIoT devices, consumer electronics and more.For engineering support or consultation, feel free to contact us.